# HTS Quasi-Particle Injection Devices for Interfaces between SFQ and CMOS Circuits

Hidehiro SHIGA<sup>†a)</sup>, Nonmember and Yoichi OKABE<sup>†</sup>, Regular Member

**SUMMARY** We have fabricated a prototype of interface devices between SFQ and CMOS circuits using HTS quasi-particle injection devices. By the injection of quasi-particles, the bridge area becomes resistive and high voltage appears at the drain electrode. As a test of device operation, we applied the signal of a function generator to the gate electrode and observed that the device successfully repeated on/off operation. We also succeeded in explaining the device characteristics by considering the thermal effects.

key words: interface, quasi-particle, SFQ, CMOS

# 1. Introduction

In the near future, superconductor single flux quantum (SFQ) computer, which is faster in operation and lower in power dissipation than the complementary metal oxide semiconductor (CMOS) computer, will be realized. Therefore, interface devices that can transmit digital data from SFQ to CMOS will become necessary.

So far, a few articles about interface circuits are reported [1]-[3]. The system can be divided in 2 components: one consists of Josephson junctions that are connected in series so that a few tens mV of voltage would be generated, and the other is a CMOS differential amplifier that can amplify the voltage to CMOS level. This kind of system is reliable and high-speed, but the circuits are complicated and the size of the system is rather large.

In this paper, we propose a new interface system that adopts quasi-particle injection devices. This system is very small and simple.

# 2. Operation Principle

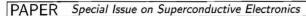

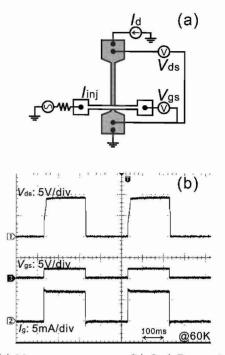

The schematic of the device and its peripheral circuits are shown in Fig. 1. Bias current  $I_d$  is previously applied to the drain electrode. When the Josephson junction that is directly connected to the gate electrode turns on, small voltage (~1 mV) is applied to the gate and consequently injection of quasi-particles to the YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-x</sub> (YBCO) bridge occurs. Then the bridge area becomes resistive and at the drain electrode high voltage appears which is large enough for CMOS circuits.

Manuscript received July 23, 2001.

Manuscript revised September 20, 2001.

# 3. Fabrication

The fabrication process is shown in Fig. 2. (1) YBCO film was deposited on  $SrTiO_3$  (STO) substrate by pulsed laser deposition (PLD) method. The thickness of the YBCO film was about 100 nm. Then, Au film was deposited in-situ, also by PLD. After that, an annealing in 1 atm O<sub>2</sub> at about 500°C was done to reduce the contact resistance between Au and YBCO. (2) The pattern of the bridge was formed by lithography and Ar ion milling. (3) Au film was deposited again by sputtering. (4) Au pattern was formed by lithography and wet etching. We used KI+I<sub>2</sub> solution to remove Au.

The length and the width of the bridge were  $100 \,\mu\text{m}$  and  $5 \,\mu\text{m}$ , respectively. The width of the Au line (injection electrode) was  $10 \,\mu\text{m}$ .

#### 4. Measurement

# 4.1 $I_{d}$ - $V_{ds}$ Characteristics

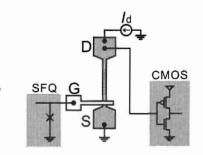

$I_{\rm d}$ - $V_{\rm ds}$  characteristics of this device is shown in Fig. 3. When  $I_{\rm d}$  exceed the critical current  $I_{\rm c}$ , the bridge becomes resistive and large voltage appears at the drain

Fig. 1 The schematic of the device and its peripheral circuits.

Fig. 2 The fabrication process.

<sup>&</sup>lt;sup>†</sup>The authors are with the Okabe laboratory, RCAST, The University of Tokyo, Tokyo, 153-8904 Japan.

a) E-mail: shiga@okabe.rcast.u-tokyo.ac.jp

**Fig. 3**  $I_{\rm d}$ - $V_{\rm ds}$  characteristics at 7 K.

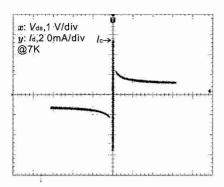

Fig. 4  $~~I_{\rm c}\text{-}I_{\rm inj}$  characteristics. The current gain is about 1.5 at its maximum.

electrode. Physical explanation of this peculiar characteristics is written in Sect. 5.1.

# 4.2 Current Gain

$I_{\rm c}$ - $I_{\rm inj}$  characteristics is shown in Fig. 4. The current gain  $\left|\frac{\Delta I_{\rm c}}{\Delta I_{\rm inj}}\right|$  is about 1–1.5.

Usual quasi-particle injection devices have barrier layer between the injector and the bridge, and that kind of devices have such large current gain as 5 or more [4], [5]. However, in order to make the contact resistance as small as possible, we made no barrier layer. Therefore the current gain remained small.

# 4.3 On/Off Operation

Using a function generator, we have tested if on/off operation is possible. The measurement system and the results are shown in Figs. 5(a), (b). When sufficient quasi-particles were injected, the bridge has become resistive and large  $V_{\rm ds}$  (about 9V) appeared. However, the voltage of injector  $V_{\rm gs}$  also rose to as high as 2V. In order to operate this device with the voltage generated by SFQ circuits,  $V_{\rm gs}$  must be kept lower than 1 mV.

Fig. 5 (a) Measurement system. (b) On/off operation of the device.  $I_{\rm d}$  was fixed to 5.5 mA. When quasi-particles were injected, large voltage as high as 9V appeared at the drain electrode.

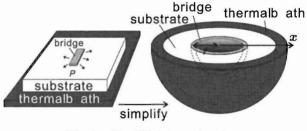

Fig. 6 Simplified thermal system.

#### 5. Discussion

#### 5.1 Device Temperature

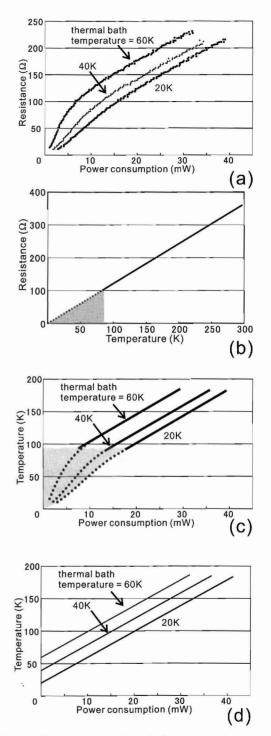

In order to explain the peculiar  $I_{\rm d}$ - $V_{\rm ds}$  characteristics shown in Fig. 3, we evaluated the device temperature.

We used a hemispherical thermal model like Fig. 6 to simplify the calculation. When power P is consumed at the bridge, the heat flux q at position x is given as follows:

$$q = \frac{P}{2\pi x^2}.$$

(1)

We can also obtain the value of the heat flux from Fourier's law

$$q = -\kappa \frac{dT}{dx},\tag{2}$$

where  $\kappa$  is the thermal conductivity of STO substrate

and T is the temperature. From these 2 equations, we obtain

$$\int_{\text{bridge}}^{\text{bath}} dT = \int_{\text{bridge}}^{\text{bath}} -\frac{P}{2\pi x^2 \kappa} dx$$

$$T_0 - T = \frac{P}{2\pi \kappa} \left[\frac{1}{x}\right]_{\text{bridge}}^{\text{bath}}.$$

(3)

If the distance from the bridge to the thermal bath is long enough (substrate thickness  $\rightarrow \infty$ ), (3) becomes

$$T = T_0 + \frac{P}{2\pi\kappa r}.\tag{4}$$

From this equation, we obtain T-P characteristics.

Then we tried to obtain T-P characteristics from the measurement results. To do so, we need resistancepower (R-P) and resistance-temperature (R-T) characteristics. R-P characteristics can be calculated using  $I_d$ - $V_{ds}$  characteristics (Fig. 7(a));  $R=V_{ds}/I_d$  and  $P=V_{ds} \times I_d$ . Figure 7(b) is R-T characteristics of the bridge. Here, it is difficult to determine R-T characteristics when the device is in operation below  $T_c$ ; they depend on the current density that flows in the bridge. The R-T curve takes its path somewhere in the gray area in Fig. 7(b). Now, by combining these two graphs, we can obtain T-P characteristics (Fig. 7(c)). T-P curve below  $T_c$  is also uncertain because of the reason mentioned above.

Next, we compared T-P characteristics obtained by two ways; by calculation and by measurement. To make Eq. (4) into a graph, we determined the thermal conductivity  $\kappa$  of the substrate so that the result would fit Fig. 7(c) and we obtained  $\kappa$ =4.5 W/m·K. According to a previous report, the thermal conductivity of SrTiO<sub>3</sub> is about 5 W/m·K [6]. Therefore this value seems to be plausible. The T-P graph when  $\kappa$ =4.5 W/m·K is shown in Fig. 7(d). This graph matches Fig. 7(c) to a large extent.

Thus, we conclude that the  $I_{\rm d}$ - $V_{\rm ds}$  characteristics can be explained by thermal effect.

#### 5.2 For Improvements

As shown in Fig. 5(b),  $V_{\rm gs}$  required to turn the bridge on is too high: it should be less than 1 mV, but 2 V is needed so far. The reason is that a part of source area near the bridge becomes resistive. In order to overcome this drawback, structure modification and downsizing is necessary. For example, if the YBCO thickness of the source area was made a few times as thick as that of the bridge area,  $V_{\rm gs}$  would be decreased drastically.

Downsizing is important not only for decreasing  $V_{\rm gs}$ , but also for faster device operation, because the response time of this device is assumed to be determined by the speed of thermal conduction.

Fig. 7 (a) R-P characteristics calculated using  $I_d$ - $V_{ds}$  characteristics. (b) R-T characteristics of the birdge. (c) T-P characteristics obtained from (a) and (b). (d) T-P characteristics obtained form Eq. (4).

# 6. Conclusion

We have fabricated HTS quasi-particle injection devices aiming at interface devices between SFQ and CMOS circuits. Using the output of a function generator as  $I_{\rm inj}$ , on/off operation was successfully performed, but the voltage needed to turn the bridge on was too high for actual use. The characteristics of the device were explained by taking the thermal effect into consideration.

#### References

- U. Ghoshal, S.V. Kishore, A.R. Feldman, L. Huynh, and T. Van Duzer, "CMOS amplifier designs for Josephson-CMOS interface circuits," IEEE Trans. Appl. Supercond., vol.5, no.2, pp.2640-2643, June 1995.

- [2] O.A. Mukhanov, S.V. Rylov, D.V. Gaidarenko, N.B. Dubash, and V.V. Borzenets, "Josephson output interface for RSFQ circuits," IEEE Trans. Appl. Supercond., vol.7, no.2, pp.2826-2831, June 1997.

- [3] N. Yoshikawa, T. Abe, Y. Kato, and H. Hoshina, "Component development for a 16 Gb/s RSFQ-CMOS interface system," IEEE Trans. Appl. Supercond., vol.11, no.1, pp.735– 738, March 2001.

- [4] T. Kobayashi, K. Hashimoto, U. Kabasawa, and M. Tonouchi, "Three terminal YBaCuO Josephson device with quasi-particle injection gate," IEEE Trans. Magn., vol.25, no.2, pp.927–930, March 1989.

- [5] C.W. Schneider, R. Moerman, D. Fuchs, R. Schneider, G.J. Gerritsma, and H. Rogalla, "HTS quasiparticle injection devices with large current gain at 77 K," IEEE Trans. Appl. Supercond., vol.9, no.2, pp.3648–3651, June 1999.

- [6] K. Nassau and A.E. Miller, "Strontium titanate: An index to the literature on properties and the growth of single crystals," J. Crystal Growth, vol.91, pp.373–381, 1988.

Hidehiro Shiga was born in Kanagawa, Japan in 1974. He received M.S. degree in Electronics Engineering from the University of Tokyo and is now a 3rd grade student of the doctor course. He is a member of JSAP.

Yoichi Okabe was born in Tokyo, Japan in 1943. He graduated from Dept. EE, Univ. of Tokyo in 1967, from Course EE, Univ. of Tokyo in 1972, and became a Ph.D. of Engineering in 1972. He is now a director of ITC and a professor of RCAST, Univ. of Tokyo, and engaged in researches on high speed and/or high functional devices, such as superconducting electronics, SQUID technology, and neural networks. He is a member of IEEJ,

IEEE, ITE, JSAP, JNNS, etc.